Achievements

差分功耗攻击(differential power attack, DPA)是一种针对密码硬件的侧信道攻击方式,是当今密码芯片的重要威胁。它通过分析密码芯片加/解密过程中的瞬时功耗特征获得参与运算的密钥信息,可以绕开密码算法的数学难题,破解密码算法。DPA攻击实施简单,仅需要简单的常用装置和PC机就可以实现,而且攻击强度高——未采取防护措施的普通密码算法芯片,攻击者采用DPA攻击,仅需要几分钟就可以获得密钥。当今日益广泛应用的各类智能卡产品(如门禁卡、付费电视卡、USB密钥、手机SIM卡等)以及加密U盘、加密硬盘等信息安全设备无一例外的都受到DPA的威胁。然而,采取抗功耗攻击措施,往往带来产品成本的增加、功耗的提高和性能的下降,阻碍了上述产品安全性的提高。清华大学在密码芯片设计技术,特别是抗功耗攻击技术方面开展多年研究,已拥有和申请多项专利,所研制的低功耗低成本抗功耗攻击方法在提供抗DPA能力的同时,能够有效控制芯片功耗和芯片面积的额外开销,适用于对成本敏感、具有低功耗要求的密码芯片产品。清华大学采用上述方法设计的两款可抗功耗攻击的AES加密算法芯片功耗水平和芯片面积均达到国际同类芯片的先进水平。我们目前面向密码芯片用户和设计企业,可提供两款适于不同应用要求的AES加密芯片或IP模块,或根据用户需要定制设计各类密码算法芯片和IP模块。

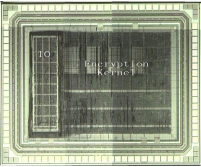

(1)Rijndael算法加密芯片THUDFAES04

功能:支持全部Rijndael加密标准,包括明文分组长度(128位、192位、256位)和密钥分组长度(128位、192位、256位)的任意组合;密钥置入后,如果下一分组不需要更换密钥则可以只输入明文分组;输入模块采用防恶意干扰设计——可以防止攻击者通过中断数据输入过程篡改密钥和利用系统内部存储单元的残存状态恢复有用信息;输入模块与输出模块彼此时钟独立,可以在同一时钟域也可以在不同时钟域。

参数:

l SMIC 0.18 微米2P6M CMOS工艺

l AES-128标准加密一个分组的能耗为0.053μJ

l 管芯面积: 2.21 mm2(含PAD)

l 吞吐率:AES-128标准下约60Mbps

图1 Rijndael算法加密芯片THUDFAES04管芯的实物照片

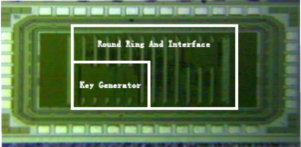

(2)AES加解密芯片THUDFAES06

功能:支持全部FIP-197标准(AES-128/192/256)的加密和解密功能;密钥置入后,如果下一分组不需要更换密钥则可以只输入明文分组;输入模块采用防恶意干扰设计——可以防止攻击者通过中断数据输入过程篡改密钥和利用系统内部存储单元的残存状态恢复有用信息;输入模块与输出模块彼此时钟独立,可以在同一时钟域也可以在不同时钟域。

参数:

l SMIC 0.18 微米2P6M CMOS工艺

l AES-128标准加密一个分组的能耗为0.019μJ(不含密钥扩展),一次128位密钥扩展的能耗是0.057μJ

l 面积: 0.43 mm2(含PAD)

l 吞吐率:AES-128标准下约20Mbps

图2 AES加解密芯片THUDFAES06管芯实物照片

THUDFAES06相对于THUDFAES04安全性更高、面积更小,适用于高安全性低吞吐率的应用。

图3 采用乱序执行技术后实际测量得到的功耗轨迹曲线

图3给出了THUDFAES04芯片执行两次相同的数据加密所测得的功耗曲线,从图中可以看到,相同的数据每次执行所产生的功耗轨迹不同,为DPA攻击制造了困难。

图4 芯片功能演示和安全性测试系统照片

上述两种芯片既可直接作为单独的芯片用于设备中,也可以提供IP核嵌入到SoC芯片中。它们既可以作为协处理器与其它处理器配合使用,也可以单独使用。芯片提供AES算法的核心加解密功能,经过扩展或主处理器控制支持各种加密模式。电路采用模块化设计,算法执行内核相对独立,输入/输出模块可根据应用单独重新设计。电路采用硬件层抗功耗攻击措施,对算法无特殊要求,该技术可以移植到其它密码算法的芯片实现。

移动安全设备、智能卡、RFID等低功耗、低成本要求的信息安全设备。

采用本算法模块在几乎不增加芯片成本的情况下能够提供高于同类普通产品的安全性和优秀的功耗性能,能够有效增强产品的竞争力。上述芯片都已经过实际加工测试验证,而且已具有经过验证的实用芯片和成熟的设计方法,无论直接应用还是根据需要定制设计都能够保证上市时间的要求,免除了企业自身的研发成本和时间。

(1)芯片供货;

(2)IP模块使用授权;

(3)成果转让;

3应用说明

4应用范围

5效益分析

6合作方式